Time to evaluate the emerging technology-CoPoS and FOPLP

CoWoS/FOWLP 轉 CoPoS/FOPLP 圓轉方的典範轉移及產業鏈分析

重點整理

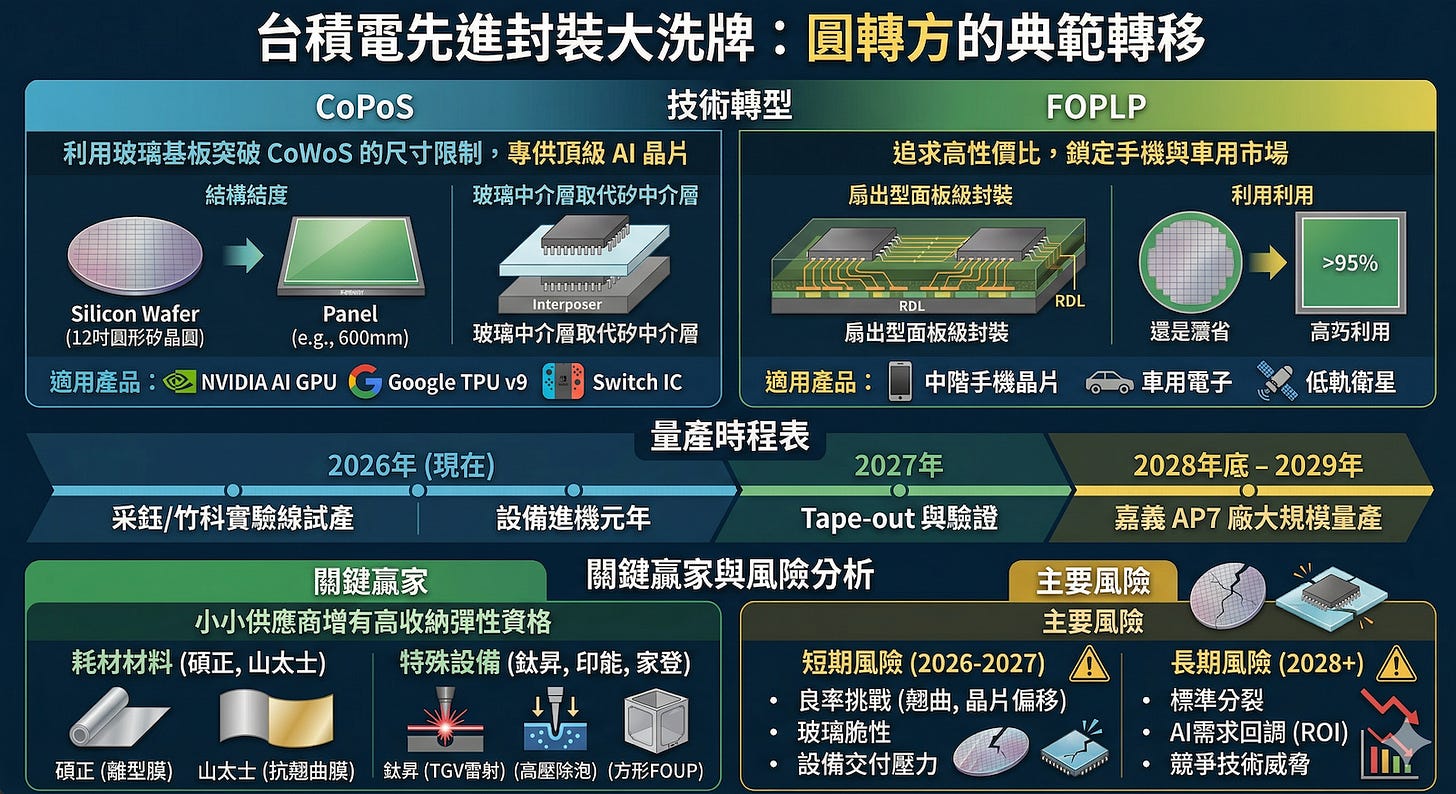

技術轉型: 台積電推動由「圓」轉「方」的封裝革命,CoPoS 利用玻璃基板突破 CoWoS 的尺寸限制,專供頂級 AI 晶片;FOPLP 則追求高性價比,鎖定手機與車用市場。

CoPoS 量產時程: 2026 年為設備進機與實驗線試產元年,預計 2028 至 2029 年在台積電嘉義 AP7 廠進入大規模量產。

關鍵贏家與風險: 營收彈性最大的是解決「翹曲」與「脫模」的材料商(山太士,碩正)及獨家設備商(鈦昇、印能、家登);主要風險在於大面積封裝的良率控制與未來 AI 需求的持續性。

CoPoS (Chip-on-Panel-on-Substrate)

CoPoS 是台積電專為超大型 AI 晶片設計的「面板級先進封裝」技術,並已正式被確立為台積電(TSMC)繼 CoWoS 之後,推動 AI 算力突破物理極限的「終極武器」。

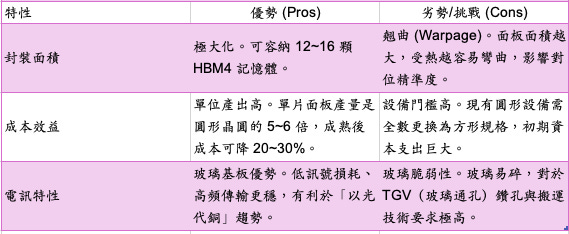

核心技術本質:它是 CoWoS 的「化圓為方」進階版。傳統 CoWoS 是在「12 吋圓形矽晶圓」上進行封裝,而 CoPoS 則是將基底換成方形面板(如 515mm x 510mm 或更大的 600mm 面板),並大量導入玻璃基板(Glass Substrate)。

取代 CoWoS-S/L(矽中介層):目前主流的矽中介層受限於光罩尺寸(Reticle Limit),面積頂多做到 3.3 倍光罩大小(約可放 8 顆 HBM)。CoPoS 透過玻璃中介層,能輕鬆突破這個限制。

技術優劣比較:

適用產品:

AI GPU:如 NVIDIA 之後的 Rubin 或 Feynman 架構 GPU(預計搭載 12-16 顆 HBM4);

AI ASIC/TPU: Google 用於自主研發的 TPU v9 世代,追求單晶片模組內最大的記憶體頻寬;

資料中心級 CPU/GPU:需要整合數十個 Chiplet 的超大型處理器;

高效能交換器晶片 (Switch):1.6T 甚至 3.2T 以上的高速網路通訊晶片。

FOPLP (Fan-out Panel-Level Packaging)

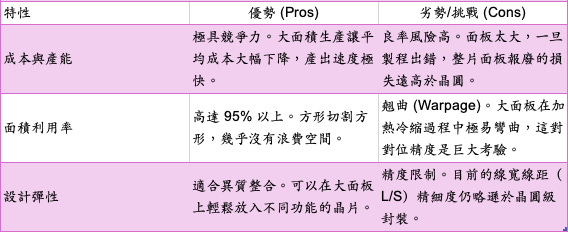

FOPLP 是一種將「扇出型封裝(Fan-Out)」與「面板生產工法」結合的技術,主要是解決圓形晶圓在邊緣產生的面積浪費,將「利用率」從 85% 提升至 95% 以上。

核心技術本質:傳統封裝是在 12 吋(300mm)的圓形晶圓上運作,而 FOPLP 則是改在巨大的方形面板(如 515x510mm 或 600x600mm)上進行。因為晶片是方形的,在圓形晶圓上會有邊角浪費;在方形面板上則能排得更滿,且單次製程處理的面積是晶圓的 5 到 7 倍。FOPLP 技術並無中介層,晶片直接嵌入模封料,透過玻璃上的RDL 互連。

取代 FOWLP(晶圓級扇出封裝)及移除ABF 載板:FOWLP(如台積電的 InFO)產能受限於 12 吋晶圓尺寸。FOPLP 透過大面積生產,能將單位成本降低約 20%~30%。對於需要多晶片整合(如 PMIC、射頻晶片、車用電子)的產品,FOPLP 可以直接在封裝層做 RDL 線路,省去昂貴的傳統載板,讓晶片更薄、效能更好。

技術優劣比較:

適用產品:

與 CoPoS 鎖定AI數據中心的AI GPU, ASIC, CPU, Switch IC 極致效能不同,FOPLP 鎖定的是「高性價比」與「大批量」的產品:

手機與消費電子:Apple 與 MediaTek (聯發科) 積極觀察 FOPLP 用於中階手機晶片與穿戴裝置;

AI 邊緣運算 (Edge AI):不需要像資料中心那麼強大,但需要低功耗、體積小的 AI 運算單元;

車用半導體:如 NXP (恩智浦)、STMicro (意法半導體)。車用晶片面積大且需要異質整合,FOPLP 的大面積與耐用性(若導入玻璃基板)極具吸引力;

低軌衛星與通訊:如 SpaceX 的射頻模組,需要大量且低成本的高頻封裝解決方案。